makelib ccstestswhich carries out all intermediate steps for all the corners and library cells. The tool suite was originally designed to test Current Source Models like CCS and ECSM. They can be used to test other type of models as well like NLDM for interpolation errors. Their purpose is to catch any timing problems before they trickle down into the design process. Its main use is to verify existing libraries and also to verify new delay calculation methods like CCS and ECSM.

One of the challenges facing designers is the accuracy and the reliability of the libraries used in the design process. Although library data is derived from Spice simulations, there could be several reasons for potential problems, especially if the test vectors used in the process are generated manually, and they are passed over to design libraries using pre-defined templates. SolutionWare tool set employ a fully automated approach to test vector generation. Design libraries are also automatically build, so a likelihood of a discrepancy between the two is extremely small. This may not be the case if the libraries are manually build or build by less automated tools. There is a possibility that timing information in design libraries like liberty may be misplaced.

Another possibility is that the cells may be under-characterized. This may happen because of state dependent nature of timing arcs and input caps. State dependency information is necessary for case analysis. During library characterization,state dependent timing arcs are identified manually or based on topologic analysis of circuit. Dynamic variation of timing and input capacitances may be accounted for.

Finally, timing information is used and interpreted by the timing analyzer. The load model used by the timing analyzer may be quite different from the lumped capacitor load model used during the characterization. This is especially true for RC network back-annotation. When used with new timing models based on Current Sources, like CCS and ECSM, it becomes necessary to be able to compare static timing analyzer delay calculation to Spice. By varying the DSPF loading, one can identify what the cause of discrepancy may be.

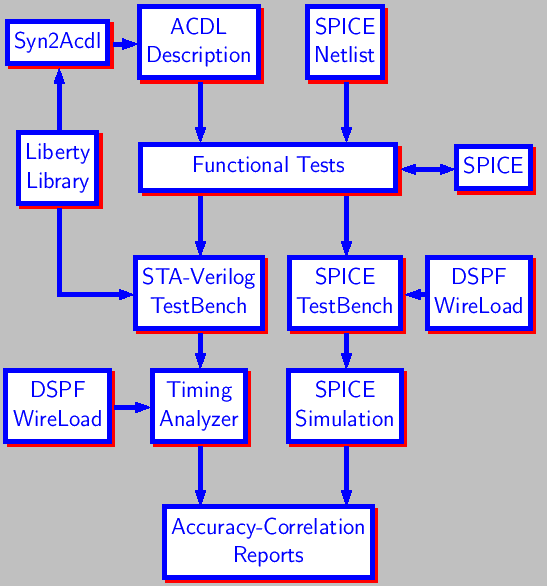

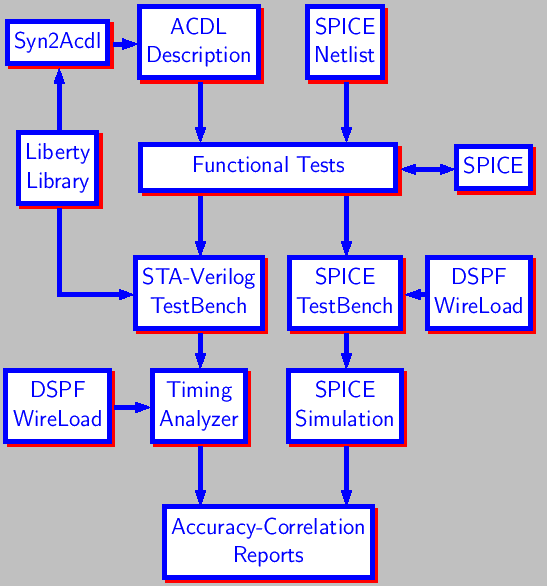

Here is the flow for comparing timing generated by a static timing analyzer to delay measured by SPICE when the cell drives a DSPF load. We assume that liberty library may be generated by some other means other than SolutionWare. Syn2acdl generates ACDL functional descriptions of the cells.

After functional tests pass, CcsTest generates a test-bench where a particular timing arc of the cell is selected and initialized. Cell drives a distributed RC network described in DSPF format. Timing analyzer uses this test-bench in Verilog format to report timing for a single timing arch. Similar test-bench is created in SPICE format, and timing delays are measured using SPICE simulation. Timing deviation is reported. Test-bench account for both driver and receiver models.